Western Digital’s RISC-V "SweRV" Core Design Released For Free

by Anton Shilov on February 15, 2019 11:30 AM EST- Posted in

- Storage

- CPUs

- SSDs

- Western Digital

- RISC-V

Western Digital has published a register-transfer level (RTL) design abstraction of its in-house designed SweRV RISC-V core. The SweRV core is one of several RISC-V projects the company as undertaken as part of their effort to spearhead the ISA, its ecosystem, and foster their own transition away from licensed, royalty-charging CPU cores. In accordance with the more open design goals of RISC-V, the publication of the high-level representation of SweTV means that third parties can use it in their own chip designs, which will popularize not only the particular core design, but also the RISC-V architecture in general.

The RTL design abstraction of Western Digital’s RISC-V SweRV core is now available at GitHub. The design is licensed under the Apache 2.0 license, which is a very permissive (and non-copyleft) license that allows the core to be used free of charge, with or without modifications, and without requiring any modifications to be released in-kind. In fact the requirements of the license are quite slim; besides requiring appropriate attribution, the only other notable restriction is that third party developers cannot use Western Digital’s brands to mark their work.

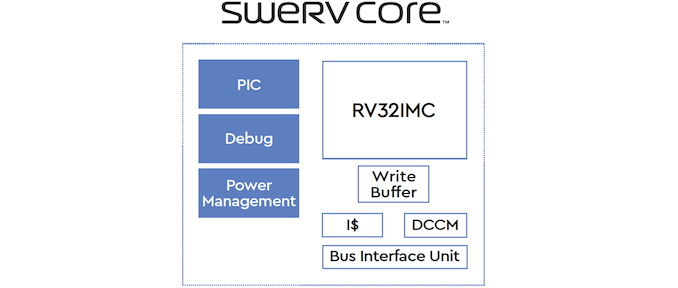

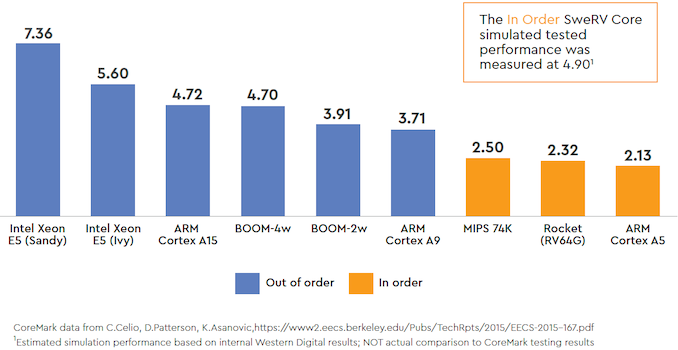

Western Digital’s RISC-V SweRV core is a 32-bit in-order core featuring a 2-way superscalar design and a nine-stage pipeline. When implemented using a 28 nm process technology, the core runs at up to 1.8 GHz. Based on Western Digital’s simulations, the SweRV core delivers 4.9 CoreMark/MHz, which is a bit higher when compared to ARM’s Cortex-A15. The developer of the core plans to use its RISC-V cores for its own embedded designs, such as flash controllers and SSDs, but it is unclear when these chips are set to be available.

Being one of the major supporters of RISC-V, Western Digital believes that by letting third-parties to use the core it will help to drive adoption of the RISC-V architecture by hardware and software designers. The latter will ensure that Western Digital’s own future designs will get a better support by software developers.

Related Reading:

- Western Digital Reveals SweRV RISC-V Core, Cache Coherency over Ethernet Initiative

- Western Digital to Use RISC-V for Controllers, Processors, Purpose-Built Platforms

- SiFive Unveils Freedom Platforms for RISC-V-Based Semi-Custom Chips

Source: Western Digital/Github

14 Comments

View All Comments

spaceship9876 - Friday, February 15, 2019 - link

I would like to see the performance of this compared to cortex a53 and a55.Wilco1 - Friday, February 15, 2019 - link

This is a simple microcontroller, not a Cortex-A53 equivalent. It's similar to a Cortex-M7 and that gets over 5 Coremarks/MHz.kfishy - Friday, February 15, 2019 - link

I mean, once you get to Cortex-M7 the lines start to blur between an applications processor and a microcontroller, to the point that NXP has started marketing a hybrid SoC called i.MX RT.Wilco1 - Friday, February 15, 2019 - link

High-end microcontrollers have become very fast indeed, with superscalar execution, caches, floating point and soon even SIMD, however a microcontroller doesn't have an MMU and can't run full Linux, so there is still a clear distinction. If you did manage to run a serious benchmark on a microcontroller (say SPEC), it would perform abysmally since it just isn't designed for that.cb88 - Thursday, March 21, 2019 - link

PIC32 MCUs do have an MMU and some of the higher end models have 32MB ram embedded, or up to 128MB ddr2 externally. They are definitely still microcontrollers though.zvonimir - Friday, February 15, 2019 - link

Paper is coming out soon. It is 5 CM/Mhz and about 3 Dhrystone MIPS/MHz. Once it is published, I will add it to GitHub. -ZvonimirZolaIII - Friday, February 15, 2019 - link

Performance is indeed very promising, more than enough for IoT and embedded. The real question would be how much gate's it is in its base layout. If it beats ARM it will skyrocket.Samus - Friday, February 15, 2019 - link

You can probably interpolate performance based on the A15 benchmark shown to reasonable accuracy, but since this isn't a performance SoC. This will likely be used in low-performance applications from Arduino to smart home devices. However, it's relatively high performance for a supplemental controller if we are to believe WD's cherry picked benchmark score :PSantoval - Friday, February 15, 2019 - link

As Wilco mentioned this core is equivalent to the "M" series of ARM cores, not their "A" series. The M series are microcontrollers, not complete SoCs.MrCommunistGen - Friday, February 15, 2019 - link

I'm a little puzzled why the Xeon E5 (Sandy) has a higher score than the Xeon E5 (Ivy).I see that the unit they are using is normalized for clock speed (score/MHz) but unless the test is multithreaded and the Sandy had more cores than the Ivy, the IVB core should have higher IPC...