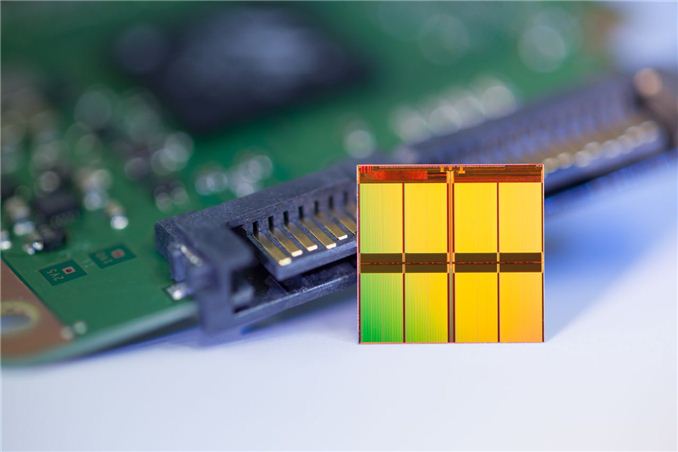

Micron Announces 16nm 128Gb MLC NAND, SSDs in 2014

by Anand Lal Shimpi on July 16, 2013 5:58 PM EST

Earlier today Micron announced its first 16nm MLC NAND device. The 128Gbit device is architecturally identical to the current 20nm/128Gbit 2-bit-per-cell MLC device that's shipping today but smaller. That means we're talking about a 16K page size and 512 pages per block (two planes). Micron didn't share many details of the new device other than to say that it'd be available in the same package (152-ball BGA 14x18mm) and feature roughly the same performance as the current 20nm part. The performance claim is an interesting one since performance typically decreases with each NAND generation as we've seen in the past. Micron's exact wording was "similiar performance" to existing 20nm 128Gbit MLC parts, which doesn't necessarily mean identical.

| Micron NAND Evolution | ||||||||||||

| 50nm | 34nm | 25nm | 20nm | 20nm | 16nm | |||||||

| Single Die Max Capacity | 16Gbit | 32Gbit | 64Gbit | 64Gbit | 128Gbit | 128Gbit | ||||||

| Page Size | 4KB | 4KB | 8KB | 8KB | 16KB | 16KB | ||||||

| Pages per Block | 128 | 128 | 256 | 256 | 512 | 512 | ||||||

| Read Page (max) | - | - | 75 µs | 100 µs | 115 µs | ? | ||||||

| Program Page (typical) | 900 µs | 1200 µs | 1300 µs | 1300 µs | 1600 µs | ? | ||||||

| Erase Block (typical) | - | - | 3 ms | 3 ms | 3.8 ms | ? | ||||||

| Die Size | - | 172mm2 | 167mm2 | 118mm2 | 202mm2 | ? | ||||||

| Gbit per mm2 | - | 0.186 | 0.383 | 0.542 | 0.634 | ? | ||||||

| Rated Program/Erase Cycles | 10000 | 5000 | 3000 | 3000 | 3000 | ~3000 | ||||||

The one bit of information that Micron is unfortunately not sharing is the actual size of its 16nm 128Gb NAND device. Citing competitive concerns, Micron is only saying that it's the industry's smallest 128Gb MLC NAND device.

Micron is targeting 3000 program/erase cycles for its 16nm NAND device. Micron's 16nm NAND is sampling now, and will be in production in the Q4 of this year. Micron expects to ship SSDs based on its 16nm NAND in 2014. If the 20nm ramp is any indication, we should expect 16nm NAND in drives in around a year from now.

10 Comments

View All Comments

TridentTrinity - Tuesday, July 16, 2013 - link

Wait a minute. Is it really 16 nm or is it one of those "1Xnm class" marketing type things with a FEOL of 16 nm and BEOL of 20 nm etc? I wonder if that is another reason they aren't mentioning size etc. Once real products are in the market it won't be long before Chipworks/UBM do their magic and reveal the data.I'm guessing the lithography for Flash products is at a different timescale/node because otherwise I haven't heard of anyone shipping digital logic devices at anything below Intel's 22nm now.

Spunjji - Tuesday, July 16, 2013 - link

The lithography for flash is indeed different, and they're not shipping, just sampling.iwod - Tuesday, July 16, 2013 - link

Lots of SSD/NAND QuestionsIt looks like 16nm will mainly be a cost drive down node then. Sell things for the same price and better margins. We will have to wait for node to mature a bit more before we see 256Gbit NAND in 2014. 10nm 512Gbit in 2015/2016.

Will NAND be on 400mm Wafers? Or would be cost of switching not justify because of the lower margin from NAND.

TLC doesn't bring much cost reduction while bringing a lot of compromise to performance and Erase Cycles. Whats the future for that? Will we see even QLC ( Quad Bit ) or even TSV like NAND where the NAND are stacked up together?

Why has Apple decided to use PCI-Express 2x instead of 4x for their Mac? Any ideas or technical reasons behind it? While Samsung manage to do the same package with PCI-E 4x.

What new SSD Controller coming soon?

MrSpadge - Wednesday, July 17, 2013 - link

"We will have to wait for node to mature a bit more before we see 256Gbit NAND in 2014. 10nm 512Gbit in 2015/2016."As long as they don't increase the interface bandwidth larger NAND dies reduce performance (fewer dies to hit a given capacity) while driving the cost for a given capacity down slightly. If you're aiming for a minimum performance target (i.e. "all channels occupied with 1 die") cost actually increases substantially, since you have to buy double the capacity!

"Will NAND be on 400mm Wafers?"

They'll move to 450 mm wafers when building new fabs at some pointin the next few years.. but don't expect any miracles.

"TLC doesn't bring much cost reduction"

Well, from my point of view the Samsung 840 is easily the best value today, and by quite some margin, unless you're expecting a heavy write load (most people should not).

"Whats the future for that? Will we see even QLC ( Quad Bit ) or even TSV like NAND where the NAND are stacked up together?"

I guess Samsung will tell us in due time. If their next mainstream SSD doesn't use TLC then that's an answer ;) QLC will surely remain reserved for memory cards etc. TSV probably doesn't help much in terms of cost savings compared to the current solution of packaging several dies together. TSV could surely make the package smaller, though.

"Why has Apple decided to use PCI-Express 2x instead of 4x for their Mac?"

Maybe their controller and NAND are not bottlenecked at 2x yet?

DanNeely - Wednesday, July 17, 2013 - link

"Why has Apple decided to use PCI-Express 2x instead of 4x for their Mac? Any ideas or technical reasons behind it? While Samsung manage to do the same package with PCI-E 4x."Product line consistency, and the limited number of pcie lanes in haswell mobile? The 15W parts only have a dozen 2.0 lanes (16 3.0 for the 28W parts); and IIRC the forthcoming 7/10W ones are only 6 or 8. With thunderbolt needing a few lanes, 802.11ac needing more than one to avoid bottle necking, that doesn't leave many lanes available for anything else.

overseer - Wednesday, July 17, 2013 - link

Would be nice if you also give typical "$ per GB" numbers in the NAND table.Minion4Hire - Wednesday, July 17, 2013 - link

So the latest and greatest NAND has to erase 8MBs worth of pages at one time? As this keeps going up won't that adversely affect write amplification?sleepeeg3 - Wednesday, July 17, 2013 - link

8MB of pages and 3,000 write cycles? At one time it was 512kb and 10,000 write cycles… Have not read any recent articles on this issue, but this has to be having a serious effect on reliability and longevity… What is the current status on this?jimhsu - Wednesday, July 17, 2013 - link

From my understanding, better write-caching algorithms and much, much larger caches (who would have thought that SSDs ship with GB-worth of memory these days, 5 years ago?) largely mitigate this problem, except in certain pathological cases. That said in typical (desktop-oriented) uses, SSDs still last much longer than the average service life of the computer they're used in. THe enterprise market is totally different, and much more expensive.iwod - Wednesday, July 17, 2013 - link

Arhaha... Thx. I didn't know the Lower Power Part Haswell has less PCI-E 3.0 lanes and Thunderport has already taken up most of those.