Flash Memory Summit, Toshiba Keynote Live Blog

by Ian Cutress & Billy Tallis on August 7, 2018 2:37 PM EST

02:42PM EDT - We're here at Flash Memory Summit! One of the first keynotes of the event is Toshiba, speaking about their use of Flash.

02:43PM EDT - Going to start in a few minutes

02:43PM EDT - But to give you a scale of Flash Memory Summit, there are around 1000+ people in the keynote hall right now

02:44PM EDT - A mix of a few press, flash vendors, and a lot of people involved in development of flash systems and deployment

02:46PM EDT - OK here we go

02:46PM EDT - Scaling Flash Technology to Meet Application Demands, presented by Jeff Ohshima, Tech Exec of SSD Application Engineering at Toshiba

02:47PM EDT - Talk about the newest flash, and flash native solutions

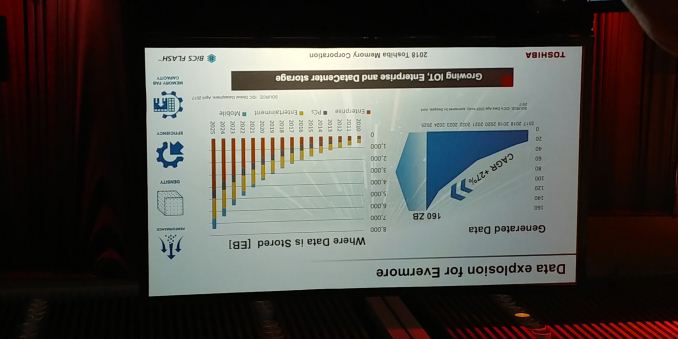

02:48PM EDT - Generated CAGR +27%, reaching 160 ZB by 2025

02:48PM EDT - Data is being mostly stored in enterprise

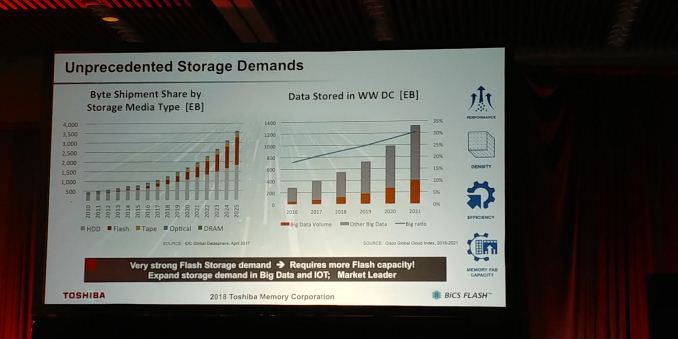

02:49PM EDT - Flash is growing in % storage bytes, almost same exabytes as HDD in 2025

02:49PM EDT - Big Data volume also expected to grow massively by 2021

02:49PM EDT - Very strong flash demand

02:49PM EDT - Big storage demands in Big Data and IoT especially, lots of growth

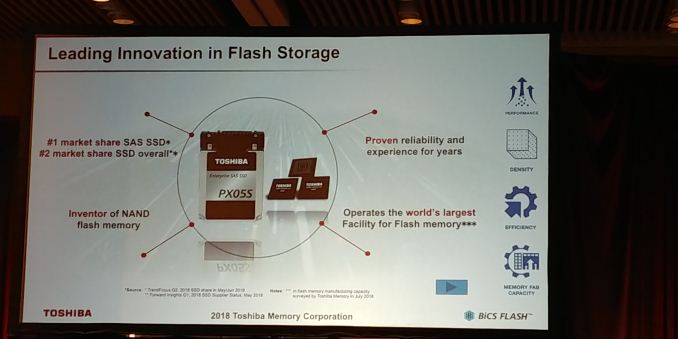

02:50PM EDT - Toshiba is number 1 in SAS, number 2 in SSD

02:50PM EDT - Constantly growing market share

02:51PM EDT - Toshiba invested NAND flash, so has lots of knowledge

02:51PM EDT - World's largest facility for flash memory

02:51PM EDT - short video of the fab

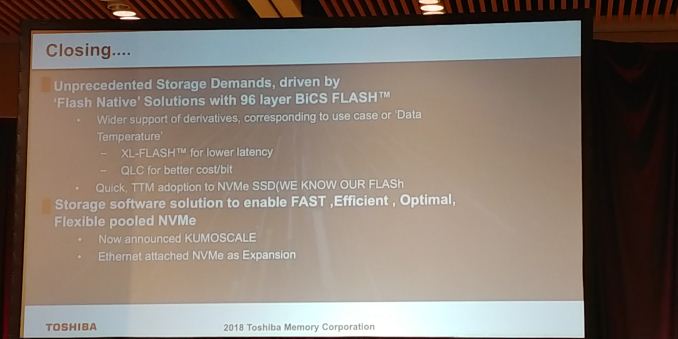

02:52PM EDT - 96-layer BiCS Flasg

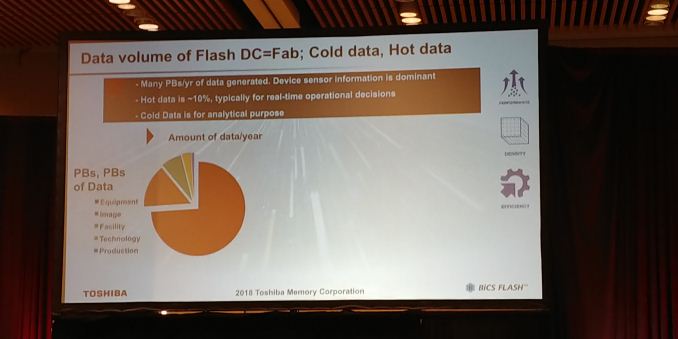

02:53PM EDT - Cold data and hot data

02:53PM EDT - Hot data is 10%, typucally for real time

02:53PM EDT - Cold data used for analytical

02:54PM EDT - Quickly grow to exabytes

02:54PM EDT - Quickly grow to exabytes

02:54PM EDT - or creating models for AI and machine learning

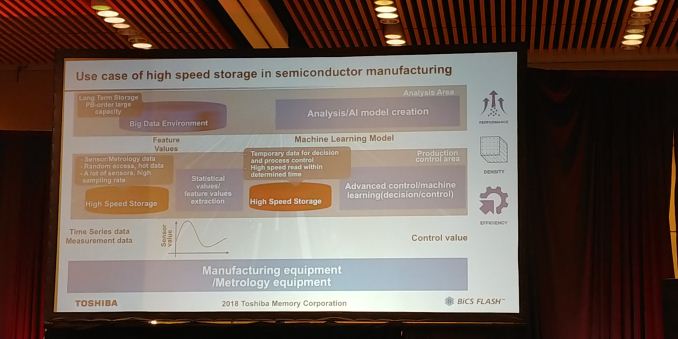

02:55PM EDT - Data is usually time series measurement data, which goes into high speed hot storage. Sometimes statistical values are extracted at this level

02:56PM EDT - data then moves into a Big Data environment for AI/ML

02:56PM EDT - Also positive feedback for model learning

02:56PM EDT - Hot data can also be used for process control and inference for real-time equipment control

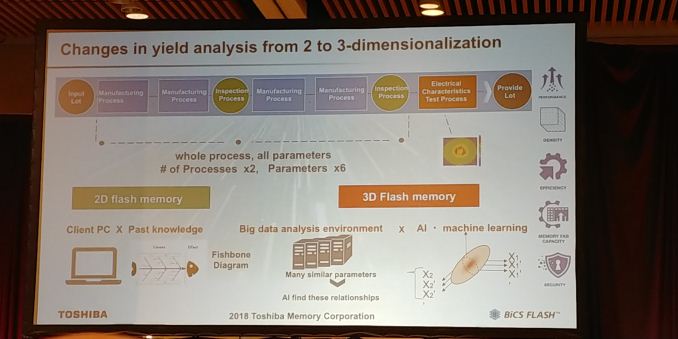

02:57PM EDT - Changes from 2D storage 3D, the number of process steps has become 2x

02:57PM EDT - Total number of process parameters is 6x

02:58PM EDT - Using past experiences to learn for future development

02:58PM EDT - Analysis has become extremely complicated

02:58PM EDT - 'We make it, we use it - it's the perfect ecosystem for flash'

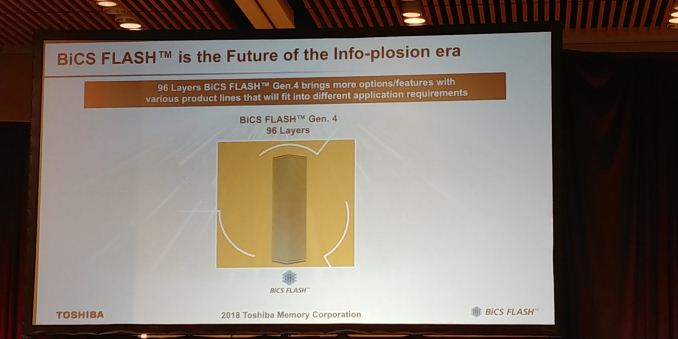

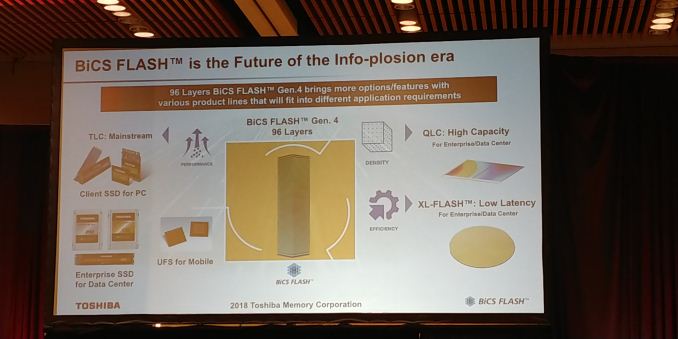

02:59PM EDT - TLC has become mainstream, 64-layer BiCS3

02:59PM EDT - Now on BiCS Gen 4, 96-layer

02:59PM EDT - Use QLC, and XL-Flash for Low Latency

03:00PM EDT - XL-Flash ahs very high speed random access latency

03:00PM EDT - XL-Flash sounds like their competitor to Samsung's Z-NAND

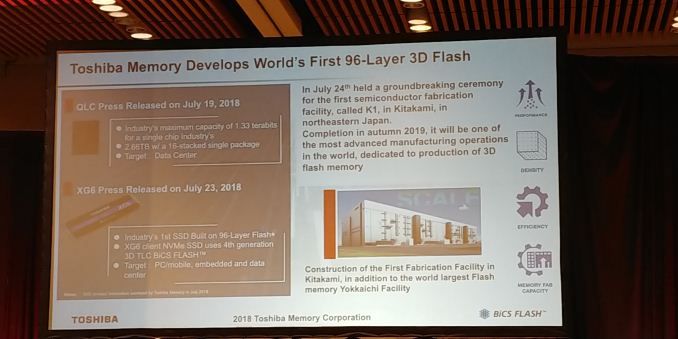

03:00PM EDT - July 24th, held a groundbreaking ceremony called K1 in Kitakami

03:01PM EDT - 3D production of Gen 4 fully

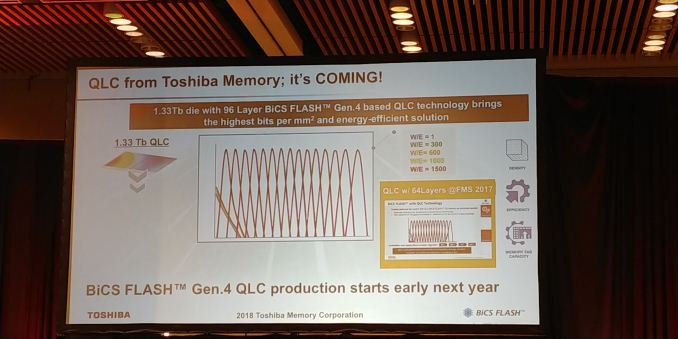

03:01PM EDT - BiCS4 QLC production starts next year

03:01PM EDT - 20TB in an M.2 22110

03:01PM EDT - or 85TB in a U.2

03:01PM EDT - 1.33 Tb QLC chips

03:02PM EDT - Good cycling up to 1500 P/E cycles

03:02PM EDT - Good opportunity with TLC portfolio

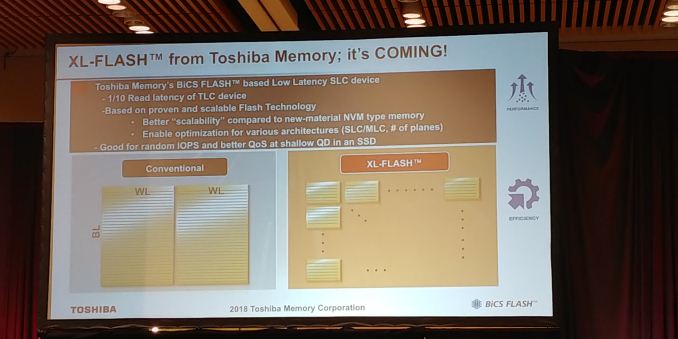

03:02PM EDT - XL-Flash has 1/10th the read latency of TLC

03:02PM EDT - XL-Flash is high-speed low-latency random read BICS

03:02PM EDT - 1/10 read latency of TLC

03:03PM EDT - Good for random IPOS and better QoS at shallow QD in an SSD

03:03PM EDT - QD = Queue Depth

03:03PM EDT - New architecture

03:03PM EDT - 'XL-Flash is just a Flash, no additional process required'

03:03PM EDT - Circuit design innovation for a memory array

03:04PM EDT - shorter bit lines and bit lines

03:04PM EDT - allowing more planes

03:04PM EDT - 2 planes vs many planes

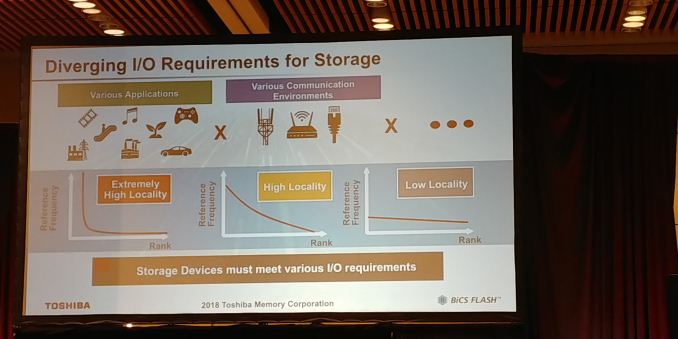

03:04PM EDT - IO is now diverging in requirements for storage

03:04PM EDT - Need to respond to market workloads

03:05PM EDT - High speed vs high-throughput

03:05PM EDT - Latency vs locality

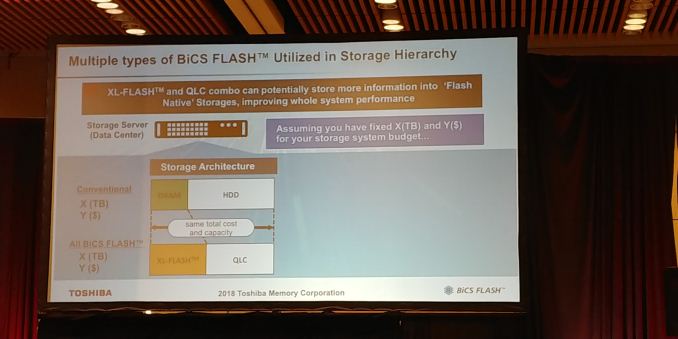

03:05PM EDT - XL-FLASH used with QLC in a combo

03:05PM EDT - 'Flash Native' storage

03:06PM EDT - Using BiCS in multiple stages

03:06PM EDT - Use XL-Flash in place of in-DRAM data ?!

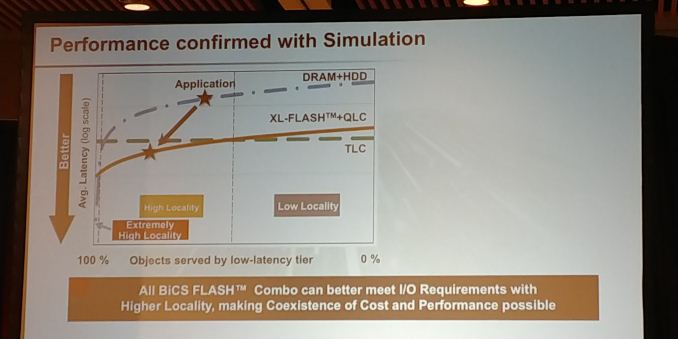

03:07PM EDT - Performance confirmed by simulation

03:07PM EDT - Meeting IO Requirements of customer use cases

03:08PM EDT - XL-Flash + QLC has lower latency than DRAM + HDD

03:08PM EDT - XL-flash can provide a larger slower cache than DRAM, with a better cache hit rate

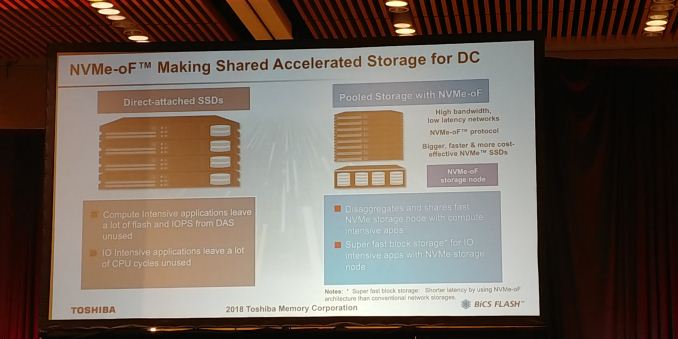

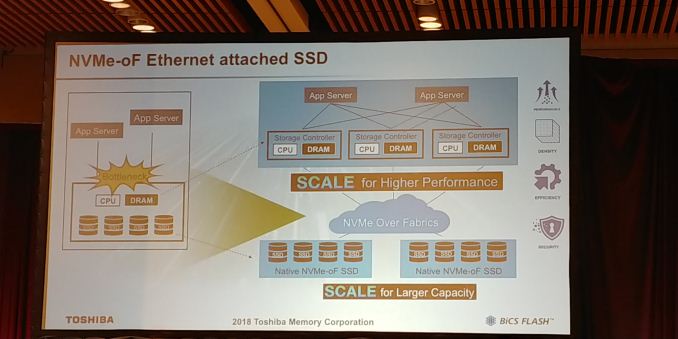

03:09PM EDT - network attached storage and NVMe over fabric

03:09PM EDT - lots of servers are idle

03:09PM EDT - Lots of IOPS left on the table

03:09PM EDT - Pooled storage with NVMe-oF allows for dynamic provisioning

03:10PM EDT - Super fast block storage, both disaggregated and abstracted

03:10PM EDT - Bringing the solution in terms of software

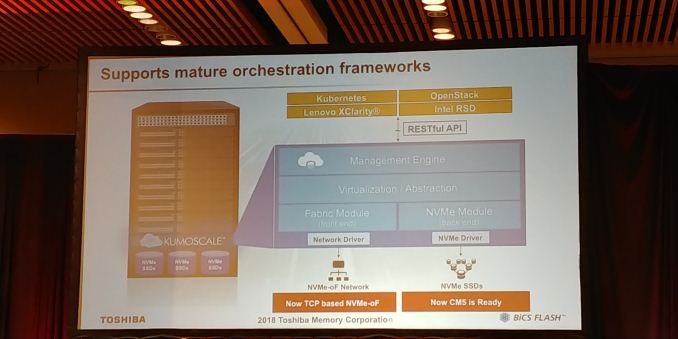

03:10PM EDT - Using KUMOSCALE

03:10PM EDT - Supports mature orchestration fameworks

03:10PM EDT - Kubernetes, XClarity, OpenStack

03:11PM EDT - Also NVMe-OF Ethernet Attached SSD

03:11PM EDT - ethernet JBOF

03:12PM EDT - New architectures of JBOF using bridge SoC by Marvell

03:13PM EDT - PCIe has internal bottlenecks on normal systems, up to 100 Gbps to 200 Gbps

03:13PM EDT - Aiming to provide total solution, 600 Gbps+

03:13PM EDT - Benefit wide range of customers

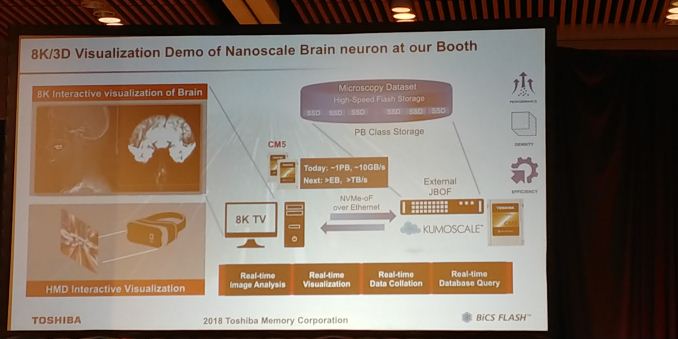

03:14PM EDT - 8K/3D visualization uses random data reads

03:14PM EDT - Solution can cover a lot of requirements

03:15PM EDT - HMD requires response to fast head movement - Toshiba has demo system for 8K HMD data

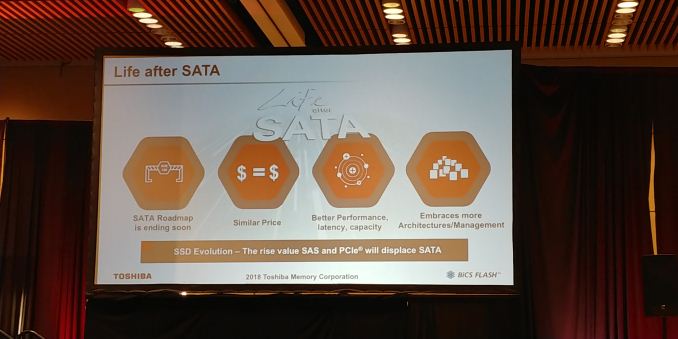

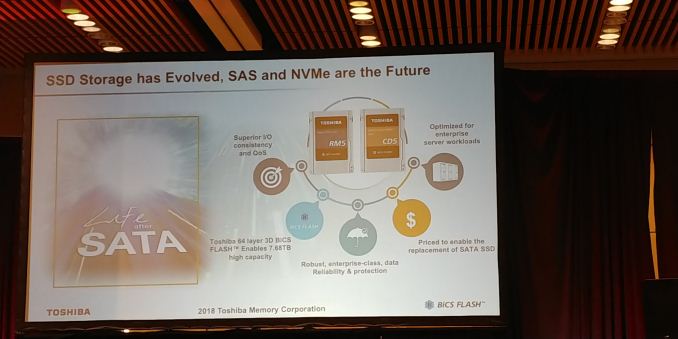

03:15PM EDT - 'Life After SATA'

03:15PM EDT - SATA Roadmap is ending soon

03:16PM EDT - NVMe and value SAS is similar price to SATA

03:16PM EDT - New drives RM5 and CD5 target life after SATA

03:16PM EDT - Quick migration from BICS3 to BiCS4

03:17PM EDT - Sale of Toshiba memory completed, merger is complete

03:18PM EDT - TMC is ready to replace SATA

03:18PM EDT - That's a wrap

1 Comments

View All Comments

bestcustomflashdrives - Thursday, March 14, 2019 - link

Nice information on flash memory summit. Keep sharing it.