Ask the Experts: ARM's Cortex A53 Lead Architect, Peter Greenhalgh

by Anand Lal Shimpi on December 10, 2013 9:00 AM EST- Posted in

- Ask the Experts

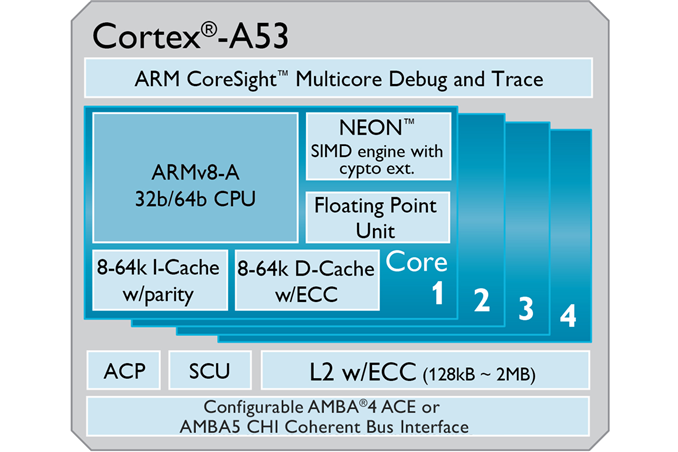

Given the timing of yesterday's Cortex A53 based Snapdragon 410 announcement, our latest Ask the Experts installment couldn't be better. Peter Greenhalgh, lead architect of the Cortex A53, has agreed to spend some time with us and answer any burning questions you might have on your mind about ARM, directly.

Peter has worked in ARM's processor division for 13 years and worked on the Cortex R4, Cortex A8 and Cortex A5 (as well as the ARM1176JZF-S and ARM1136JF-S). He was lead architect of the Cortex A7 and ARM's big.LITTLE technology as well.

Later this month I'll be doing a live discussion with Peter via Google Hangouts, but you guys get first crack at him. If you have any questions about Cortex A7, Cortex A53, big.LITTLE or pretty much anything else ARM related fire away in the comments below. Peter will be answering your questions personally in the next week.

Please help make Peter feel at home here on AnandTech by impressing him with your questions. Do a good job here and I might be able to even convince him to give away some ARM powered goodies...

158 Comments

View All Comments

theduckofdeath - Saturday, December 14, 2013 - link

I concur with everyone else on this one, ddriver. You are really wrong about this. Just because a data segment might be 2GB, you still need a L3 cache for all of those machine code level commands that actually do something with that 2GB chunk of data.Krysto - Thursday, December 12, 2013 - link

In that case, there's also Cortex A57, which will be faster than anything Atom can do.But my guess is he was referring to energy efficiency, and if the extreme energy efficiency of Cortex A53 can be more useful in servers than perhaps Cortex A57.

JoannWDean - Saturday, December 14, 2013 - link

my buddy's aunt earned 14958 dollar past week. she been working on the laptop and got a 510900 dollar home. All she did was get blessed and put into action the information leaked on this site... http://cpl.pw/OKeIJoshodanshok - Tuesday, December 10, 2013 - link

Hi, it would be interesting to know two thing:- the cache memories (L1/L2) are write-back or write-through? Inclusive or exclusive?

- multiprocessor capabilities are limited to 4 cores or they can scale to 8+ cores without additional glue logic?

Thanks.

SleepyFE - Tuesday, December 10, 2013 - link

Hi.I know the second one. The new big.LITTLE spec allows the use of all 8+ cores.

fteoath64 - Thursday, December 12, 2013 - link

The cache cogency bus (CCN) supports a maximum of 8 cpu-id per socket. That is why.L2 cache is actually a RAM accelerator. Filling cache with data (in and out) allows for interleaved and delayed writes to slow memory at roughly the cache speed. This means an order of magnitute faster since most L2 cache are 95% hits anyways. Branch-prediction logic will reduce the stalling of the pipeline and cache misses, thus enhancing the performance. Yes, server apps needs lots of RAM mean the cache size and efficiency is vitally important there ...

Peter Greenhalgh - Wednesday, December 11, 2013 - link

Hi Shodanshok,All cacheable attributes are supported, but Cortex-A53 is optimised around write-back, write-allocate. The L2 cache is inclusive on the instruction side and exclusive on the data side.

A Cortex-A53 cluster only supports up to 4-cores. If more than 4-cores are required in a platform then multiple clusters can be implemented and coherently connected using an interconnect such as CCI-400. The reason for not scaling to 8-cores per cluster is that the L2 micro-architecture would need to either compromise energy-efficiency in the 1-4 core range to achieve performance in the 4-8 core range, or compromise performance in the 4-8 core range to maximise energy-efficiency in the 1-4 core range. This isn’t a hard and fast rule for all clusters, but is the case for a cluster at the Cortex-A53 power/performance point. For the majority of mobile use cases it is best to focus on energy efficiency and enable more than 4-cores through multi-cluster solutions.

shodanshok - Wednesday, December 11, 2013 - link

Thank you very much Peter :)lukarak - Tuesday, December 10, 2013 - link

We have seen MediaTek introducing an 8xA7 SOC, instead of going to the big.LITTLE configuration of some sorts. Do you expect the same thing to happen with the A53 and A57 generation for low budget SOCs or will this generation's combo be a little easier and cheaper to implement?Krysto - Tuesday, December 10, 2013 - link

If it includes A57, it's high-end by default. That chip you're talking about isn't big.Little, nor does it contain Cortex A15 in it. It's an 8-core Cortex A7 chip, so yes, I assume Mediatek will make another 8-core one with Cortex A53, but I wouldn't exactly call it high-end, more like mid-to high-end.